# **Application Note**

# Digibridge Operation and Measurement Technique

Just how does a Digibridge work? Automatic LCR meters like the 1689 Digibridge use analog techniques to detect the in-phase and quadrature components of the unknown's impedance. "Unknown" and "DUT" refer to the device under test. This information is then used to calculate other parameters of interest (R, L, C, Q etc.). Read on to discover what's inside a QuadTech 1689 Digibridge and how it makes and calculates impedance measurements.

#### **Basic Techniques**

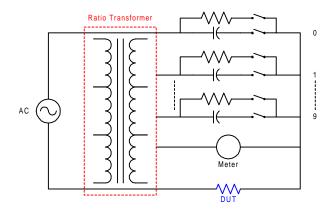

Early commercial LCR "bridges" used a variety of techniques involving the matching or "nulling" of two signals derived from a single source. The first signal generated by applying the test signal to the unknown and the second signal generated by utilizing a combination of known-value R and C standards. The signals were summed through a detector (normally a panel meter with or without some level of amplification). When zero current was noted, it could be assumed that the current magnitude through the unknown was equal to that of the standard and that the phase was exactly the reverse (180° apart). The combination of standards selected could be arranged to read out C and D<sub>F</sub> directly as in the IET Model 1620 and 1621 Capacitance Bridges. Automatic bridges have generally not used the nulling technique but rely on a combination of microprocessor control and phase sensitive detectors.

Figure 1: Ratio Transformer Method of Null Detection

### The Phase Sensitive Detector

The balanced bridge detector is not well suited to automation due to the many sensitive nodes that must be switched to achieve a null. In the late 1970s H.P. Hall of GenRad Instruments introduced his design of a synchronous detector circuit to solve this problem. Mr. Hall's synchronous detector invention was granted U.S. Patent # 4,181,949.

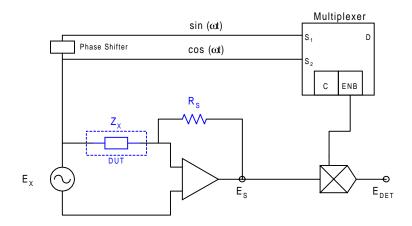

Whereas the null detector uses a combination of precisely known standards, the synchronous detector utilizes a single (reference) resistor ( $R_S$ ) of relatively low accuracy. The detector operates by gathering either the in-phase or quadrature component of the current through the unknown. This is accomplished by multiplying the current by the sine of the stimulus for the in-phase component or the cosine for the quadrature.

Figure 2: Basic Synchronous Detector Circuit

Depending upon which input to the multiplexer is selected, the detector voltage,  $E_{DET}$ , will represent  $E_S$  [sin ( $\omega t$ )] or  $E_S$  [cos ( $\omega t$ )]. Since the voltage applied is known, the admittance of the DUT, as a complex vector, can be calculated.  $Z_X = R_S$  ( $E_X/E_S$ ). From the admittance, any desired parameter may be calculated.

In order for the technique to be effective, the arithmetic requires that:

- 1. The current representation, Es, and the sine wave being multiplied are synchronous to the stimulation signal Ex. Any phase relationship between the signals is acceptable as long as it is constant throughout the detection time.

- 2. The multiplication is performed over an integer number of cycles.

## Implementation Difficulties

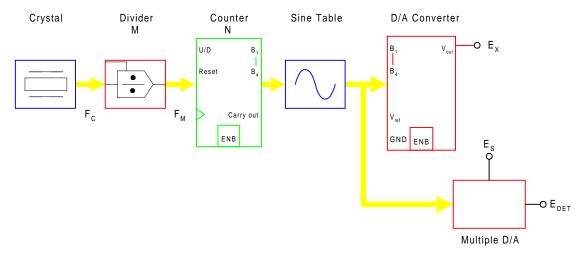

The technique of choice for multiplying the two signals has been to use a multiplying D/A converter. The signal, Es, is applied to the reference input of the D/A and a series of binary numbers representing a sine or cosine wave are applied to the digital input. In order to achieve synchronization, the sine wave stimulus is generated by applying the identical binary stream to a second D/A converter.

Figure 3: Digital Sine Wave Generation and Synchronous Detection

The method of using the same binary stream to drive both D/A's simultaneously assures perfect synchronization. This implementation has worked well providing flexible, automatic measurement capability with a high degree of precision and speed. It has two factors that have limited its effectiveness: the bandwidth of the multiplying D/A, and the ability of the source to generate frequencies with a high degree of resolution. Multiplying four quadrant D/A's with bandwidth above a few hundred kilohertz is simply not available at reasonable cost.

The frequency generation scheme provides synchronization by using a ROM look-up table to drive both D/A's. A binary counter that repeatedly counts from 0 to N drives this ROM look-up table. N is the size of the look-up table and is typically in the range of 64-1024. The frequency of the sine wave is  $F_C/(M \cdot N)$ . The difficulty is that the division is integer, and not all frequencies can be produced.

For a sine table of size 256, and a crystal frequency of 38.6 MHz, the following may be produced:

| M=1 | f=150 kHz |

|-----|-----------|

| M=2 | f=75 kHz  |

| M=3 | f=50 kHz  |

As can be inferred from the above example, no combination of crystal frequency and N will produce all desired frequencies in a general-purpose meter. If one is willing to reduce the number of "sample points" from the look-up ROM (resulting in more noise) the value of N can be adjusted in concert with M to provide additional values. In practice there have always been a large number of desirable values of f that can only be approximated.

# The 1689 Digibridge Measurements & Calculations

This Digibridge® RLC tester uses a patented measurement technique, in which a microprocessor calculates the desired impedance parameters from a series of 6 or 8 voltage measurements (6 for FAST, 6 for MED, and 8 for SLOW measurement rates.) These measurements include quadrature (90 degree) and inverse (180 degree) vector components of the voltages across the device under test Zx (the DUT), and across a standard resistor Rs carrying the same current as the DUT. Each of these voltage measurements is meaningless by itself, because the reference signals have no particular phase relationship to the measured analog signals, and because the current through Zx is not controlled. Each set of voltage measurements is made in rapid sequence with the same phase-sensitive detector and analog-to-digital converter. Therefore properly chosen differences between these measurements subtract out fixed offset errors, and ratios between them cancel out the value of the common current, the scale factor of the detector-converter, and the effect of the relative reference-to-signal phase angle.

The phase-sensitive detector uses 4 reference signals, precisely 90 degrees apart, that have exactly the same frequency as the test signal, but whose phase relationship to any of the analog voltages or currents (such as the current through Zx and Rs) is incidental. Therefore, no precise analog phase shifter or waveform squaring circuit is required. Correct phase relationships are maintained by generating test signal and reference signals from the same high-frequency source.

Because of the measurement technique and circuitry, the only calibration adjustment in the Digibridge is the factory setting of the test-voltage-level reference. The only precision components in this instrument are four standard resistors and a quartz-crystal stabilized oscillator. There is no reactance standard. For example, C and D are calculated by the microprocessor from the set of voltage measurements, the predetermined frequency, and the calibrated R and Q of the applicable standard resistor.

In these calculations, the microprocessor automatically removes from the measured result the parameters of the test connection ("stray" capacitance and conductance and series resistance and inductance), if simple open-circuit and short-circuit "ZERO" calibration measurements have been performed by the operator. The values obtained during "ZERO" calibration are stored in Digibridge memory and retained during power-down and power-up.

The impedance of each internal standard resistor is similarly stored in memory for use by the microprocessor in the calculation of parameters being measured. (For this purpose, the Digibridge measures its own internal standard resistors against an external standard during factory calibration – and recalibration, if any.) Therefore, the impedances of the internal resistance standards are known at the calibration frequency (usually 1 kHz), and are computed by the microprocessor for other test frequencies.

The Digibridge also stores the frequency error of its crystal-referenced oscillator (actual versus nominal frequency, expressed in parts per million) so that the microprocessor uses a corrected frequency value in each calculation of capacitance or inductance from measured impedance. This frequency correction is programmed into the Digibridge during factory calibration – and recalibration, if any.

## 1689 Detector & Control Circuits

The microprocessor controls the measurement sequence, according to programs in the read-only memory, using stored operator selections that are made available through keyboard control or (if the interface option is installed) by remote-control command. Selections include for example – parameters: R and Q, L and Q, C and D, or C and R; test voltage: .005 to 1.275 V; equivalent circuit: series or parallel; test rate: SLOW, MEDIUM, or FAST; frequency: programmable from 12 Hz to 100 kHz in 503 steps; delay: up to 99999 ms; and averaging: 2 to 255 measurements; etc.

The instrument normally auto-ranges to find the correct range; but operation can be restricted to any of the four ranges (1, 2, 3, 4), under keyboard control. Each range is 4 octaves wide (16:1), with reduced-accuracy extensions both above and below.

Leading zeroes before the decimal point are blanked out of the RLC and QDR displays.

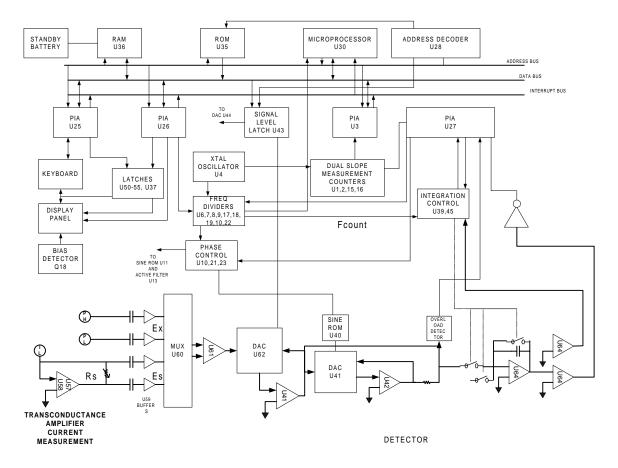

Figure 4: Block Diagram Detector and Control Circuits

The block diagram in Figure 4 illustrates the microprocessor in the upper center connected by data and address buses to digital circuitry including memories (RAM and ROM) and peripheral interface adaptors (PIAs).

### 1689 Sine Wave Generator

Analog circuitry is shown in the lower part of the Figure 4 and Figure 5, where Zx is supplied with a test signal at frequency f from a sine-wave generator, driven by a crystal-controlled digital frequency divider circuit. The P/I signal selector and instrumentation amplifier supply an analog signal that represents 2 impedances alternately: the appropriate internal resistance standard, Rs, and the DUT, Zx.

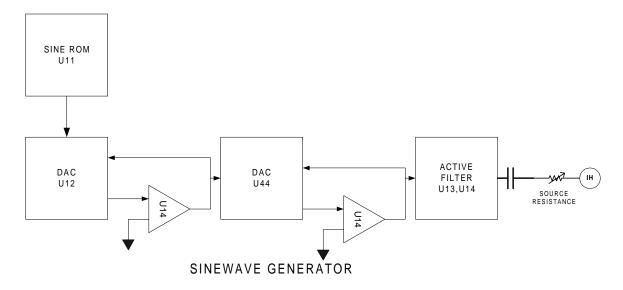

Figure 5: Block Diagram Sine Generator

The phase-sensitive (dual-slope) detector and measurement counters convert this analog signal into digital form. Refer to the circuit descriptions herein for more information.

From this information and criteria selected by the keyboard (or remote control), the microprocessor calculates the RLC and QDR values for display, averaging, bin assignments, etc. The 1689M Digibridge calculates faster than the 1689 Digibridge.

#### **Elementary Measurement Circuit**

The measurement technique is illustrated by the accompanying simplified diagram, which can be correlated with the previous (block) diagram. A sine-wave generator drives current Ix through the DUT Zx and standard resistor Rs in series. Two differential amplifiers with the same gain K produce voltages Es and Ex. Simple algebra, some of which is shown in the figure, leads to the expression for the "unknown" impedance:

$$Zx = Rs [Ex/Es]$$

Notice that this ratio is complex. Two values (such as C and D or L and Q) are automatically calculated by the microprocessor from Zx, frequency, and other information.

# **1689 Circuit Descriptions**

#### Sine-Wave Generator

Sine wave generator: Given square waves at frequencies of 64 f, 32 f, 16 f, 8 f, 4 f, 2 f, and f, a ROM containing the mathematical sine function drives a D/A converter to form a finely stepped approximation to a sine wave at frequency f. The filter provides smoothing of the test signal.

Source of the Test Signal: Starting with a digital signal at 64 times the selected test frequency, the sine wave generator provides the test signal that drives a small but essential current through the DUT. The sine wave is generated as follows.

Binary dividers count down from 64 f, providing signals at 32 f, 16 f, .... 2f, f. This set of signals is used to address a read-only memory that contains a 64-step approximation to a sine function. The ROM output (as an 8-bit binary number) is converted by a D/A converter to a stepped approximation of a sine wave, which is then smoothed by filtering before its use in the measurement of a DUT. The filter is switched approximately, according to the selected test frequency.

Source of the Reference Sine Wave for the Multiplying Detector: Another sine-function ROM is addressed by the same digital signals (64 f through f) to produce another stepped approximation of a sine wave at 0 degrees. Suitable inversions of signals 2f and/or f serve to shift the phase of the output sine wave, under microprocessor control, by 90, 180, or 270 degrees.

#### The Dual-Slope Integrating Detector and Converter (See Figure 4.)

Circuitry: The phase-sensitive detector/converter circuit consists of a multiplier whose dc output is measured by a dual-slope converter, providing the measurement in digital form. The multiplier is a multiplying D/A converter whose "reference" input is the test signal and whose digital controls are signals representing a stepwise approximation of a reference sine wave at the test frequency. The dc value of the multiplier output is proportional to the product of signal magnitude multiplied by the cosine of the phase angle between the test signal and the reference sine wave.

The dual-slope converter includes these three stages: dual-slope integrator, comparator, and counter (all controlled by the microprocessor through PIAs). In the dual-slope integrator, a capacitor is charged for a controlled integration time interval (sampling) at a rate proportional to the multiplier output voltage. This capacitor is then discharged at a fixed rate (the de-integration slope) to zero voltage, a condition that is sensed by a comparator. (Refer to signal going from U64 to Integration Control in Figure 4). Thus, the integrator and comparator transform the sampled dc output from the multiplier into a precise interval of time. The dual-slope measurement counter is gated by this time interval, this converting it into a digital number, which is a principal data input to the microprocessor.

# 1689 Integration Time & Data Acquisition Time

If the integration time is relatively long, so that the integration capacitor voltage reaches a certain reference level, another comparator triggers the beginning of the return (de-integration) slope before sampling has been completed. (Refer to signal output of U64 going to the inverter in Figure 4). The detector is then sampling and converting simultaneously for a portion of the dual-slope conversion cycle.

#### **Data Acquisition Time**

Data acquisition time includes pauses for synchronization, and several integration/de-integration cycles. A pause for synchronization varies depending on timing relationships among the START signal, length of settling time or programmed delay, length of the previous integration/de-integration cycle, and the Digibridge clocks (particularly FCOUNT, shown on block diagram). This pause can be as much as one test-frequency period for high frequencies or up to 1/32 of the test-frequency period for low frequencies.

The integration (sampling, gate, or capacitor charging) time of the dual=slope integrator is the number of full periods of the test frequency whose sum is closest to (4 ms) x (integration-time factor) for MEDIUM, or closest to but not over 100 ms for SLOW measurement rate. (The integration-time factor is normally 1.0 but can be programmed between 0.25 and 6).

The return (de-integration) time depends on the dc voltage being converted and whether the output of U64 going to the inverter has been triggered (Figure 4); therefore, this time requirement varies in a complex manner.

Data acquisition includes several complete dual-slope conversion cycles, with the reference sine wave at 3 or 4 different phases, exactly 90 degrees apart, as follows:

For FAST and MEDIUM rates, 6 cycles (2 each with reference phases of 0, 90, and 180). For FAST and MEDIUM rates if "quick acquisition" special function is enabled, 5 cycles. For SLOW measurement rate, 8 cycles (2 each with ref phases of 0, 90, 180, and 270).

Therefore, data acquisition time is complex, discontinuous function of test frequency, the selected measurement rate, programmed integration-time factor, enabling or disabling of "quick acquisition", and pauses for synchronization.

This amount of information may seem complicated but the truth is that the 1689 Digibridge uses straightforward analog measurements and a microprocessor to calculate the desired impedance parameter. A deceptively simple yet highly accurate measuring technique.

For complete product specifications on the 1689 Digibridge or any of QuadTech's products, visit us at <a href="http://www.quadtech.com/products">http://www.quadtech.com/products</a>. Call us at 1-800-253-1230 or email your questions to info@quadtech.com.

The information presented here is subject to change and is intended for general information only **©QuadTech, Incorporated**

Telephone: 1- 800-253-1230, Website: <a href="http://www.quadtech.com">http://www.quadtech.com</a>

Printed in U.S.A.

P/N 035129/A1

September 2003